在高速PCB設計中,如何通過仿真工具驗證鋪銅對信號完整性的影響?

來源:m.amoherb.com.cn 作者:領卓PCBA 發布時間:2026-02-28 09:35:41 點擊數: 關鍵詞:PCB設計

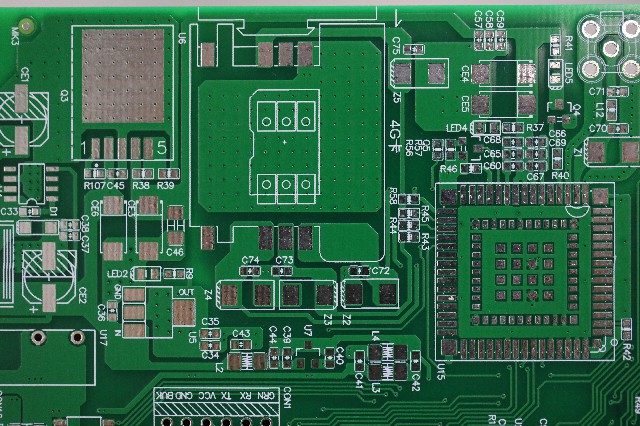

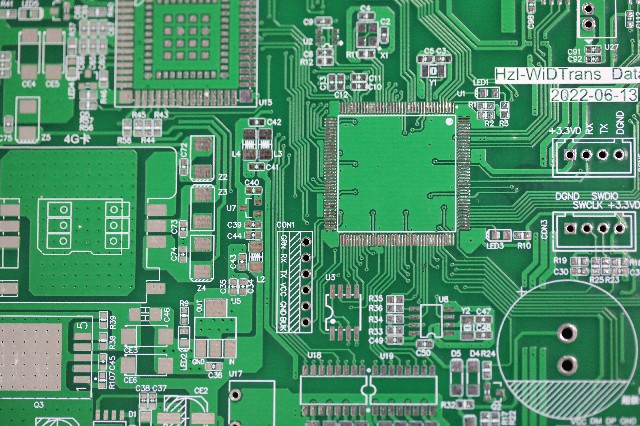

23年PCBA一站式行業經驗PCBA加工廠家今天為大家講講在高速PCB設計中,如何通過仿真工具驗證鋪銅對信號完整性的影響。在高速PCB設計中,鋪銅(Plane)并非簡單的“接地”或“鋪滿銅皮”,它本質上是信號回流路徑和參考平面的核心組成部分。通過仿真工具驗證其影響,是確保信號完整性(SI)的關鍵步驟。

高速PCB設計通過仿真工具驗證鋪銅對信號完整性的影響

一、 仿真前的模型準備:如何“畫”出真實的鋪銅

仿真結果的準確性,首先取決于你導入的模型是否真實反映了鋪銅的物理特性。

關鍵設置項 | 正確做法(避免坑點) | 錯誤做法(導致仿真失真) |

|---|---|---|

銅皮類型 | Dynamic

Shape(動態銅皮):仿真前必須Update

to Smooth(更新光順)。靜態銅皮(Static)需檢查是否與過孔/焊盤正確避讓。 | 使用未更新的動態銅皮(存在dummy

net或空洞),或忽略銅皮與過孔的短路/斷路。 |

介質材料 | 明確指定Core(芯板)和Prepreg(PP片)的Dk(介電常數)和Df(損耗角正切)。鋪銅的粗糙度(Surface

Roughness)必須設置(如Huray模型)。 | 使用默認的“理想導體”(Perfect

Conductor)或忽略粗糙度,這會導致插損(IL)仿真過于樂觀。 |

疊層與厚度 | 精確設置每層鋪銅的厚度(如1oz=35um)。注意:表層鋪銅因蝕刻通常比內層薄,且因綠油覆蓋需修正有效Dk。 | 所有層使用同一厚度,忽略制造工藝帶來的厚度變化。 |

過孔反焊盤 | 必須保留。反焊盤(Anti-pad)是鋪銅上的隔離孔,它的尺寸決定了過孔的寄生電容(C_via)。刪除它等于將過孔直接短路到平面,仿真會完全錯誤。 | 為了“好看”或“DRC通過”而刪除反焊盤,或在2D視圖下誤刪。 |

操作提示:在Allegro中,使用Export -> IPC2581 或 Auto Export to Sigrity 通常比傳統的.brd 文件能保留更完整的鋪銅和材料信息。

二、 仿真驗證的三大核心場景

鋪銅對信號的影響主要體現在“回路”上。你需要針對以下三種場景分別設置仿真:

場景1:驗證參考平面連續性(最致命的影響)

問題:信號線在換層時,如果第二層沒有完整的鋪銅(被分割或鏤空),回流路徑會被迫繞遠路,產生巨大的電感,引發阻抗突變和邊沿振鈴。

仿真方法:

提取拓撲:提取包含換層過孔的完整鏈路(Driver -> Via -> Receiver)。

TDR仿真:

工具:Sigrity TDR/TDT, ADS TDR。

觀察點:在阻抗曲線上,重點關注過孔區域。良好的鋪銅會顯示平滑的阻抗曲線(如50Ω±10%)。若出現阻抗尖峰(如飆升至70-80Ω)或塌陷,說明反焊盤過大(電容小)或參考平面不連續(電感大)。

眼圖仿真:

在平面不連續點,眼圖會呈現明顯的閉合(高度減小)或雙線(重影,源于反射)。

場景2:驗證電源噪聲耦合(PDN阻抗)

問題:相鄰層的信號線會通過鋪銅之間的平板電容耦合電源噪聲。同時,鋪銅的諧振(諧振腔效應)會在特定頻率點放大噪聲。

仿真方法:

Power-Aware SI(如Sigrity PowerSI):

在提取S參數時,勾選“Include Power/Ground Nets”。

對比“僅考慮GND”和“同時考慮Power/Gnd”兩種模式下的S21(插損)和S11(回損)。在諧振頻率點(如1GHz附近),有電源噪聲參與的仿真通常插損會惡化(凹陷更深)。

Z參數(阻抗)分析:

在電源分配網絡(PDN)仿真中,查看VCC鋪銅的Z11阻抗曲線。目標是在目標頻段(如0-100MHz)保持低阻抗。如果鋪銅距離過遠或去耦電容不足,阻抗曲線會過早地“抬頭”。

場景3:驗證跨分割影響(Return Path)

問題:信號線跨越鋪銅的分割間隙(如模擬地AGND和數字地DGND之間的裂縫)。

仿真方法:

場求解器(3D EM):使用HFSS 3D Layout或CST。

建模時,刻意保留一條跨越分割的微帶線。

結果:觀察電場分布圖(E-Field)。你會看到信號在跨分割點,電場線會“噴射”出來,繞很遠的路才能找到回流點,而不是緊貼信號線下方。這直觀證明了EMI輻射的增大。

量化指標:查看該情況下的差模轉共模(Sdc21/Sdc11)參數,數值會顯著惡化。

三、 關鍵仿真結果解讀與判斷標準

仿真類型 | 健康指標(Good) | 危險指標(Bad,需修改鋪銅) | 修改鋪銅的應對策略 |

|---|---|---|---|

TDR阻抗 | 過孔處阻抗波動

< ±10%(如45Ω-55Ω)。 | 過孔處阻抗

> +20% 或 < -30%(如>60Ω或<35Ω)。 | 1.

減小反焊盤(增加電容,壓低阻抗)。 2. 在換層處附近添加GND過孔(Stitching Via)為回流提供捷徑。 |

S參數(S21) | 在奈奎斯特頻率(0.5*Data

Rate)處,插損 < -3dB。 | 在低頻段(如100MHz)就出現深凹陷(Notch),或整體插損曲線嚴重下移。 | 1.

避免跨分割,確保參考平面完整。 2. 更換低Df的板材,或加粗線寬降低損耗。 |

眼圖 | 眼高

> 閾值電壓的20%,眼張 > UI的60%。 | 眼圖完全閉合,或出現明顯的“雙眼皮”(雙線)。 | 1.

修改鋪銅形狀:在敏感信號下方填充“禁布銅”的空白區域。 2. 調整疊層:將信號層夾在兩個實心鋪銅層之間(Stripline),避免表層微帶線參考層太遠。 |

四、 實用技巧與避坑指南

不要迷信“全板鋪銅”:對于>10Gbps的信號,表層的隨機碎銅(Floating Shape)會像天線一樣耦合噪聲。仿真時,如果表層有無關的孤島銅皮,刪除它們往往能改善眼圖。

仿真邊界(Boundary)設置:在3D EM工具中,如果鋪銅是無限大的理想平面,結果會很好;但實際PCB尺寸有限,需將仿真邊界設置為輻射邊界(Radiation)或PML,以模擬邊緣反射,這樣結果更真實。

直流壓降(DC Drop):對于電源鋪銅,別忘了運行DC仿真。薄的鋪銅在遠距離供電時,電壓會掉到芯片工作電壓以下,導致芯片失效。仿真會直接顯示“紅色”危險區域。

總結:鋪銅仿真的核心邏輯是“讓電子回家(回流)的路更順暢”。通過TDR看阻抗連續性,通過S參數看頻域諧振,通過3D場看路徑分布。一旦仿真發現異常,優先修改的不是走線,而是調整鋪銅的形狀、疊層順序和過孔間距。

關于在高速PCB設計中,如何通過仿真工具驗證鋪銅對信號完整性的影響的知識點,想要了解更多的,可關注領卓PCBA,如有需要了解更多PCBA打樣、PCBA代工、PCBA加工的相關技術知識,歡迎留言獲取!

熱門動態

-

什么是SMT貼片加工回流焊?SMT貼片加工回流焊工藝介紹

時間:2026 瀏覽:27

-

SMT貼片加工價格核算需要考慮哪些因素?影響SMT貼片報價的因素

時間:2026 瀏覽:27

-

PCBA加工中如何根據產品尺寸和層數來精確選擇Tg值?PCBA加工中選擇Tg值邏輯

時間:2026 瀏覽:27

-

PCB打樣厚度該怎么選擇?PCB打樣時厚度選擇需考慮的因素

時間:2026 瀏覽:27

-

PCBA打樣整套流程有哪些?PCBA打樣從設計到成品交付流程

時間:2026 瀏覽:27

-

PCB設計中如何減少ESD損害?PCB設計中減少ESD損害的技巧

時間:2026 瀏覽:27

-

消費電子PCBA代工廠家領卓怎么樣?領卓消費電子PCBA代工廠家

時間:2026 瀏覽:27

-

PCBA加工有鉛工藝與無鉛工藝差異有哪些?PCBA加工有鉛工藝與無鉛工藝的六大差異

時間:2026 瀏覽:27

-

PCBA加工如何選擇更適合的工藝?SMT與DIP在PCBA加工中的差異解析

時間:2026 瀏覽:27

-

SMT貼片加工中元件位移的原因有哪些?SMT貼片加工中元件位移原因

時間:2026 瀏覽:27

搜索

搜索